# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2019/0198565 A1

Jun. 27, 2019 (43) Pub. Date:

### (54) LIGHT EMITTING STACKED STRUCTURE AND DISPLAY DEVICE HAVING THE SAME

(71) Applicant: SEOUL VIOSYS CO., LTD., Ansan-si

(72) Inventors: Chung Hoon Lee, Ansan-si (KR); Jong Hyeon Chae, Ansan-si (KR); Seong Gvu Jang, Ansan-si (KR); Ho Joon Lee, Ansan-si (KR)

(21) Appl. No.: 16/228,621

(22) Filed: Dec. 20, 2018

## Related U.S. Application Data

(60) Provisional application No. 62/609,186, filed on Dec. 21, 2017, provisional application No. 62/618,573, filed on Jan. 17, 2018.

#### **Publication Classification**

(51) Int. Cl. H01L 27/15 (2006.01)G09G 3/32 (2006.01)

#### G09G 3/20 (2006.01)H01L 33/50 (2006.01)H01L 33/30 (2006.01)H01L 33/40 (2006.01)

(52) U.S. Cl.

CPC ...... H01L 27/156 (2013.01); G09G 3/32 (2013.01); G09G 3/2003 (2013.01); H01L *33/504* (2013.01); *G09G 2300/0452* (2013.01); H01L 33/405 (2013.01); G09G 2310/0267 (2013.01); G09G 2310/08 (2013.01); H01L *33/30* (2013.01)

#### (57)**ABSTRACT**

A light emitting stacked structure including a plurality of epitaxial sub-units disposed one over another, each of the epitaxial sub-units configured to emit different colored light, in which each epitaxial sub-unit has a light emitting area that overlaps one another, and at least one epitaxial sub-unit has an area different from the area of another epitaxial sub-unit.

FIG. 1

FIG. 2

FIG. 4

FIG. 6

FIG. 8

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 16

**FIG. 17**

FIG. 18

FIG. 19

**FIG. 20**

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28

FIG. 29

FIG. 30

FIG. 32

FIG. 33

FIG. 34

FIG. 35

**FIG. 36**

**FIG. 37**

FIG. 38

FIG. 39

## FIG. 40A

FIG. 40B

## **FIG. 40C**

**FIG. 40D**

**FIG. 41A**

FIG. 41B

FIG. 41C

**FIG. 42A**

**FIG. 42B**

**FIG. 43A**

FIG. 43B

**FIG. 44A**

FIG. 44B

FIG. 45A

FIG. 45B

FIG. 46A

**FIG. 46B**

**FIG. 47A**

FIG. 47B

FIG. 48A

FIG. 48B

FIG. 49A

FIG. 49B

**FIG. 50A**

FIG. 50B

FIG. 51

**FIG. 52A**

**FIG. 52B**

FIG. 53

FIG. 54

# LIGHT EMITTING STACKED STRUCTURE AND DISPLAY DEVICE HAVING THE SAME

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims priority from and the benefit of the U.S. Provisional Application No. 62/609,186, filed on Dec. 21, 2017, and the U.S. Provisional Application No. 62/618,573, filed on Jan. 17, 2018, which are hereby incorporated by reference for all purposes as if fully set forth herein.

#### **BACKGROUND**

#### Field

[0002] Exemplary embodiments of the invention relate to a light emitting stacked structure and a display device having the same and, more specifically, to a micro light emitting device having a stacked structure and a display device having the same.

#### Discussion of the Background

[0003] A display device that implements an image using a light emitting diode (LED) has been recently developed. The display device employing the light emitting diode may include red, green, and blue light emitting diodes individually grown on a substrate.

[0004] As an inorganic light source, light emitting diodes have been used in various technical fields, such as displays, vehicular lamps, general lighting, and the like. With advantages of long lifespan, low power consumption, and high response speed, light emitting diodes have been rapidly replacing an existing light source.

[0005] Light emitting diodes have been mainly used as a backlight light source in a display apparatus. However, a micro-LED display has been developed as a next generation display that is capable of implementing an image directly using the light emitting diodes.

[0006] In general, a display apparatus implements various colors by using mixed colors of blue, green and red light. The display apparatus includes pixels each having subpixels that correspond to blue, green, and red colors, and a color of a certain pixel may be determined based on the colors of the sub-pixels therein, and an image can be displayed through combination of the pixels.

[0007] In a micro-LED display, micro-LEDs corresponding to each subpixel are arranged on a two-dimensional plane. Therefore, a large number of micro LEDs are required to be disposed on one substrate. However, the micro-LED has a very small size with a surface area of about 10,000 square Lm or less, and thus, there are various problems due to this small size. In particular, it is difficult to mount the micro-LEDs on a display panel due to its small size, especially as over hundreds of thousands or millions are required.

[0008] In addition, there is a need for a high-resolution and full-color display device, as well as for a display device having a high level of color purity and color reproducibility that can be manufactured in a simplified method.

[0009] The above information disclosed in this Background section is only for understanding of the background of the inventive concepts, and, therefore, it may contain information that does not constitute prior art.

#### **SUMMARY**

[0010] Light emitting stacked structures constructed according to the principles and some exemplary implementations of the invention are capable of increasing a light emitting area of each subpixel without increasing the pixel area.

[0011] Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention have a simple structure that is capable of being manufactured in streamlined steps. For example, a plurality of pixels may be formed at the wafer level by wafer bonding, thereby eliminating the need for individual mounting of light emitting diodes.

[0012] Additional features of the inventive concepts will be set forth in the description which follows, and in part will be apparent from the description, or may be learned by practice of the inventive concepts.

[0013] A light emitting stacked structure according to an exemplary embodiment includes a plurality of epitaxial sub-units disposed one over another, each of the epitaxial sub-units configured to emit different colored light, in which each epitaxial sub-unit has a light emitting area that overlaps one another, and at least one epitaxial sub-unit has an area different from the area of another epitaxial sub-unit.

[0014] The area of each epitaxial sub-unit may decrease along a first direction.

[0015] Between two adjacent epitaxial sub-units, an upper epitaxial sub-unit may completely overlap a lower epitaxial sub-unit having a larger area.

[0016] Light emitted from each epitaxial sub-unit may have different energy bands from each other, and the energy bands may increase along a first direction.

[0017] The epitaxial sub-units may be independently drivable.

[0018] Light emitted from a lower epitaxial sub-unit may be configured to be emitted to the outside of the light emitted stacked structure by passing through an upper epitaxial sub-unit disposed on the lower epitaxial sub-unit.

[0019] The upper epitaxial sub-unit may be configured to transmit at least about 80% of light emitted from the lower epitaxial sub-unit.

[0020] The epitaxial sub-units may include a first epitaxial stack configured to emit a first color light, a second epitaxial stack disposed on the first epitaxial stack and configured to emit a second color light having a wavelength band different from the first color light, and a third epitaxial stack disposed on the second epitaxial stack and configured to emit a third color light having a wavelength band different from the first and second color lights.

[0021] The first, second, and third color lights may be a red light, a green light, and a blue light, respectively.

[0022] Each of the first, second, and third epitaxial stacks may include a p-type semiconductor layer, an active layer disposed on the p-type semiconductor layer, and an n-type semiconductor layer disposed on the active layer.

[0023] The light emitting stacked structure may further include first, second, and third p-type contact electrodes connected to the p-type semiconductor layers of the first, second, and third epitaxial stacks, respectively.

[0024] The light emitting stacked structure may further include a substrate disposed under the first epitaxial stack, in which the first p-type contact electrode may be disposed between the substrate and the first epitaxial stack.

[0025] The light emitting stacked structure may further include first, second, and third n-type contact electrodes connected to the n-type semiconductor layers of the first, second, and third epitaxial stacks, respectively.

[0026] The light emitting stacked structure may further include a common line applying a common voltage to the first, second, and third p-type contact electrodes, and first, second, and third light emitting signal lines applying a light emitting signal to the first, second, and third n-type contact electrodes, respectively.

[0027] The light emitting stacked structure may further include at least one of a first wavelength pass filter disposed between the first epitaxial stack and the second epitaxial stack and a second wavelength pass filter disposed between the second epitaxial stack and the third epitaxial stack.

[0028] The light emitting diode pixel may include a micro LED having a surface area less than about 10,000 square  $\mu m$ . [0029] At least one of the first, second, and third epitaxial stacks may have a concave-convex pattern formed on one surface thereof.

[0030] A display device according to an exemplary embodiment includes a plurality of pixels, at least one of the pixels including a light emitting stacked structure including a plurality of epitaxial sub-units disposed one over another, each of the epitaxial sub-units configured to emit different colored light, in which each epitaxial sub-unit has a light emitting area that overlaps one another, and at least one epitaxial sub-unit has an area different from the area of another epitaxial sub-unit.

[0031] The display device may be configured to be driven in a passive matrix manner.

[0032] The display device may be configured to be driven in an active matrix manner.

[0033] A light emitting diode pixel for a display according to an exemplary embodiment includes a first LED sub-unit, a second LED sub-unit disposed on a first portion of the first LED sub-unit, and a third LED sub-unit disposed on a second portion of the second LED sub-unit, in which each of the first, second, and third LED sub-units include a first conductivity type semiconductor layer and a second conductivity type semiconductor layer, light generated from the first LED sub-unit is configured to be emitted outside of the light emitting diode pixel through a third portion of the first LED sub-unit different from the first portion, and light generated from the second LED sub-unit is configured to be emitted outside of the light emitting diode pixel through a fourth portion of the second LED sub-unit different from the second portion.

[0034] The first LED sub-unit, the second LED sub-unit, and the third LED sub-unit may be configured to emit light having different wavelengths from each other, respectively.

[0035] The first, second, and third LED sub-units may include first LED stack, second LED stack, and third LED stack configured to emit red light, green light and blue light, respectively.

[0036] The light emitting diode pixel may further include a first reflection layer interposed between the first LED stack and the second LED stack to reflect light emitted from the first LED stack back to the first LED stack, and a second reflection layer interposed between the second LED stack and the third LED stack to reflect light emitted from the second LED stack back to the second LED stack.

[0037] The light emitting diode pixel may further include a first transparent insulation layer interposed between the

first LED stack and the first reflection layer, and a second transparent insulation layer interposed between the second LED stack and the second reflection layer.

[0038] The light emitting diode pixel may further include a first bonding layer interposed between the first reflection layer and the second LED stack, and a second bonding layer interposed between the second reflection layer and the third LED stack.

[0039] Each of the first and second bonding layers may include metal.

[0040] The light emitting diode pixel may further include a first upper ohmic electrode contacting the first conductivity type semiconductor layer of the first LED sub-unit, a first lower ohmic electrode contacting the second conductivity type semiconductor layer of the first LED sub-unit, a second upper ohmic electrode contacting the first conductivity type semiconductor layer of the second LED sub-unit, a second lower ohmic electrode contacting the second conductivity type semiconductor layer of the second LED sub-unit, a third upper ohmic electrode contacting the first conductivity type semiconductor layer of the third LED sub-unit, and a third lower ohmic electrode contacting the second conductivity type semiconductor layer of the third LED sub-unit, in which the first upper ohmic electrode may contact the first conductivity type semiconductor layer of the first LED sub-unit in a portion of the first LED sub-unit different from the first portion, and the second upper ohmic electrode may contact the first conductivity type semiconductor layer of the second LED sub-unit in a portion of the second LED sub-unit different from the second portion.

[0041] The first lower ohmic electrode may include a first reflective layer disposed under the first LED sub-unit.

[0042] The first lower ohmic electrode, the second lower ohmic electrode, and the third lower ohmic electrode may be electrically connected to a common line.

[0043] Each of the second lower ohmic electrode and the third lower ohmic electrode may include a second reflective layer and a third reflective layer, respectively.

[0044] The first reflective layer may be configured to reflect light emitted from the first LED sub-unit, and the second reflective layer is configured to reflect light emitted from the second LED sub-unit.

[0045] The light emitting diode pixel may include a micro LED having a surface area less than about 10,000 square  $\mu m$ .

[0046] The first LED sub-unit may be configured to emit any one of red, green, and blue light, the second LED sub-unit may be configured to emit any one of red, green, and blue light different from light emitted from the first LED sub-unit, and the third LED sub-unit may be configured to emit any one of red, green, and blue light different from light emitted from the first and second LED sub-units.

[0047] The third portion of the first LED, the fourth portion of the second LED sub-unit, and the third LED sub-unit may not overlap each other.

[0048] At least one of the first, second, and third upper ohmic electrodes may include a pad portion and a projection extending therefrom.

[0049] The pad portion may have a substantially circular shape, and the projection may have a substantially elongated shape.

[0050] The projections of the first, second, and third LED stub-units may be substantially parallel to each other in a plan view.

[0051] The first LED sub-unit may surround the third LED sub-unit in a plan view.

[0052] A display apparatus may include a plurality of pixels arranged on a support substrate, at least one of the pixels including the light emitting diode pixel according to an exemplary embodiment.

[0053] It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory and are intended to provide further explanation of the invention as claimed.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0054] The accompanying drawings, which are included to provide a further understanding of the invention and are incorporated in and constitute a part of this specification, illustrate exemplary embodiments of the invention, and together with the description serve to explain the inventive concepts.

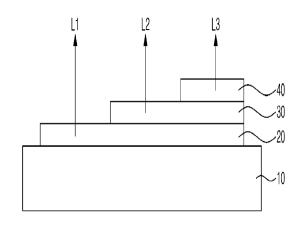

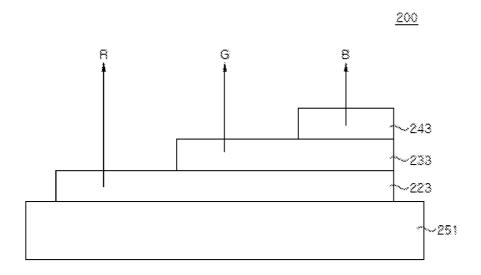

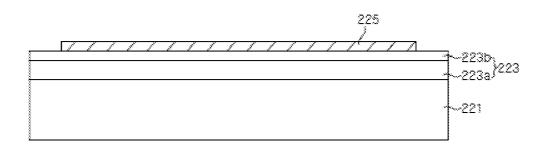

[0055] FIG. 1 is a schematic cross-sectional view of a light emitting stacked structure constructed according to an exemplary embodiment.

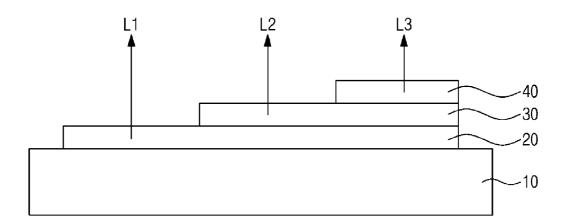

[0056] FIG. 2 is a cross-sectional view of a light emitting stacked structure according to an exemplary embodiment.

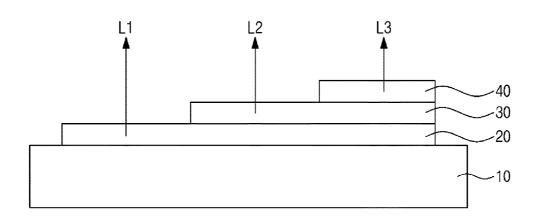

[0057] FIG. 3 is a schematic cross-sectional view of a light emitting stacked structure according to an exemplary embodiment.

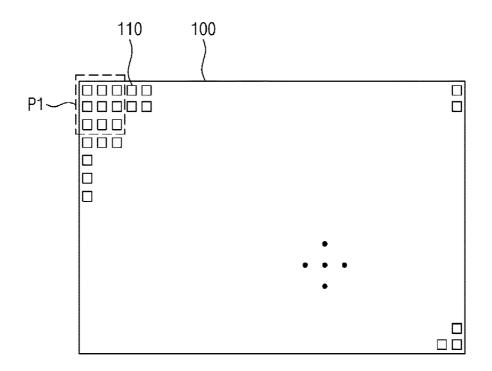

[0058] FIG. 4 is a plan view of a display device according to an exemplary embodiment.

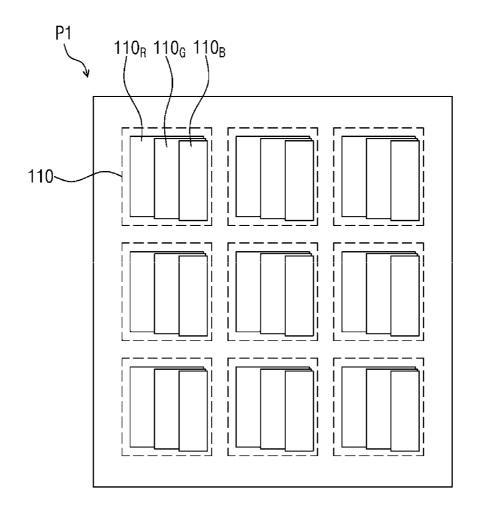

[0059] FIG.  $\tilde{\mathbf{5}}$  is an enlarged plan view of portion P1 of FIG. 4.

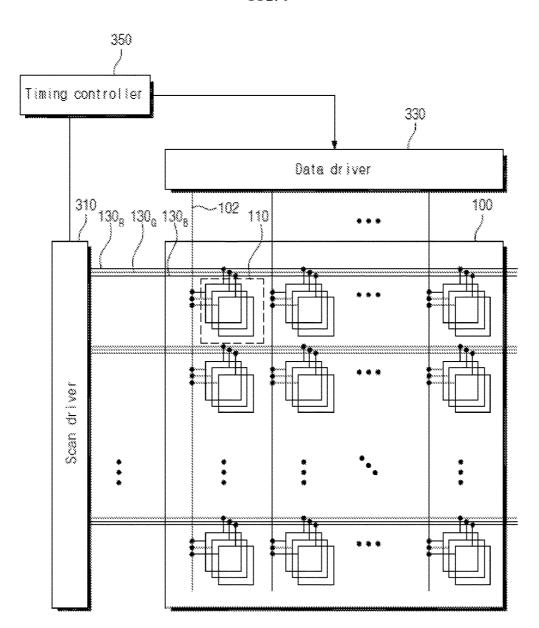

[0060] FIG. 6 is a block diagram of a display device according to an exemplary embodiment.

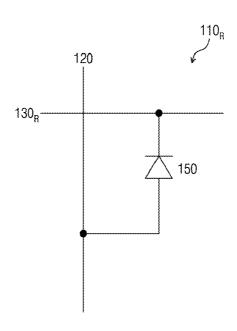

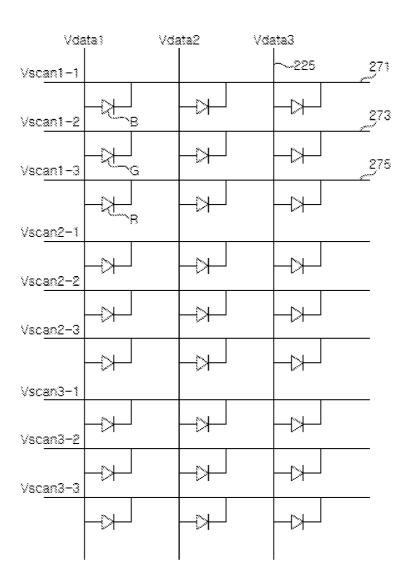

[0061] FIG. 7 is a circuit diagram of one pixel for a passive matrix type display device according to an exemplary embodiment.

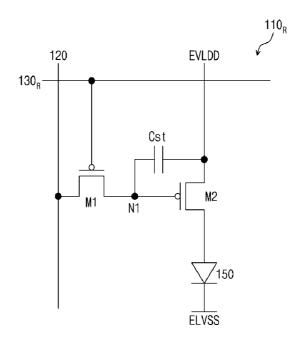

[0062] FIG. 8 is a circuit diagram of one pixel for an active matrix type display device according to an exemplary embodiment.

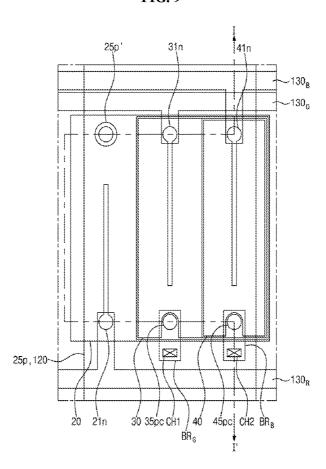

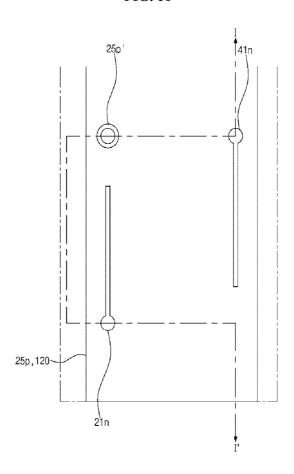

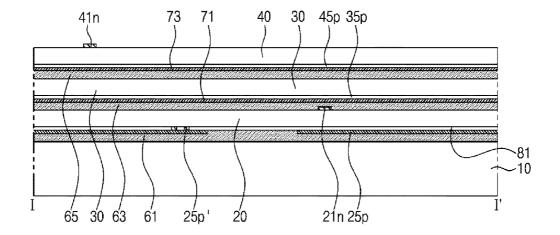

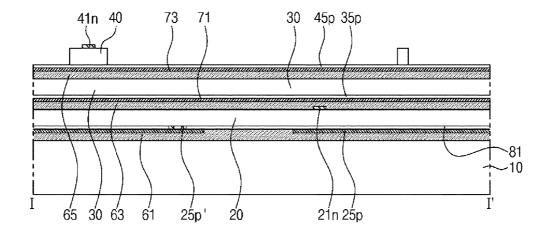

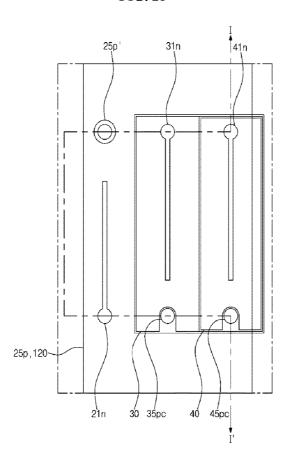

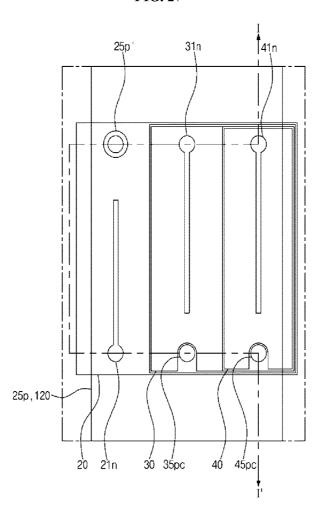

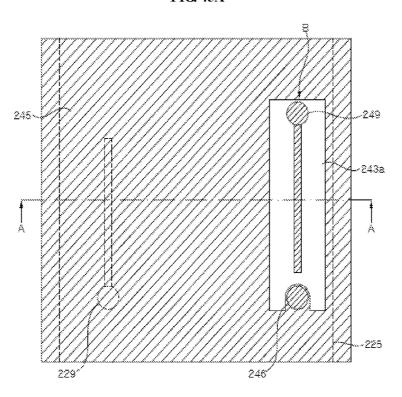

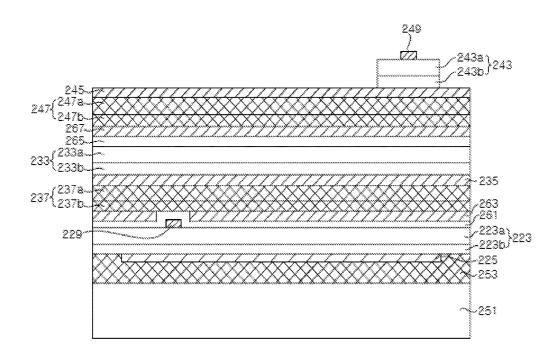

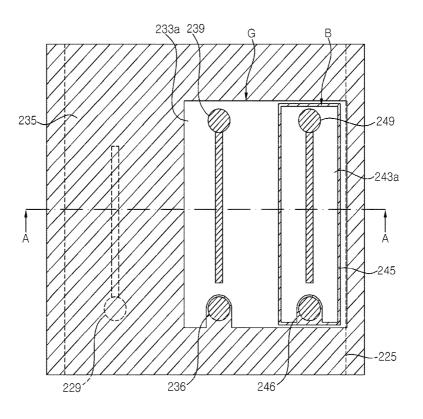

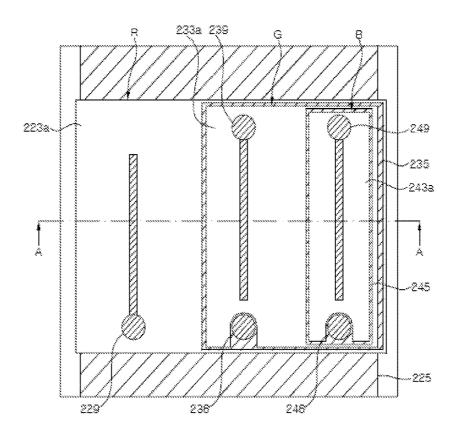

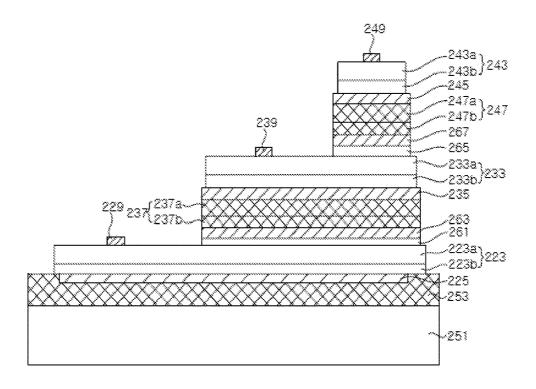

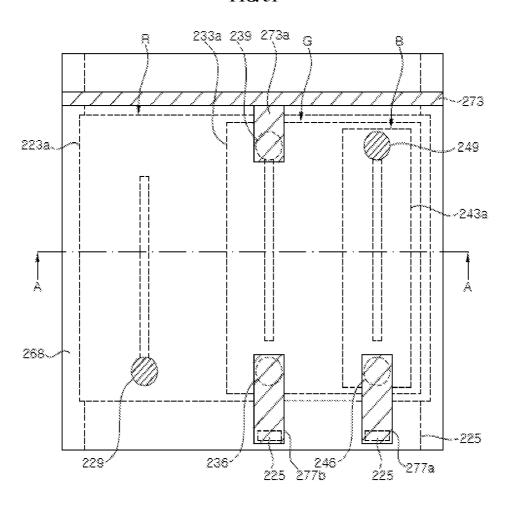

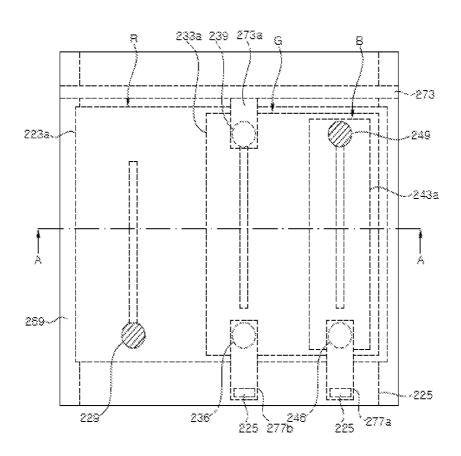

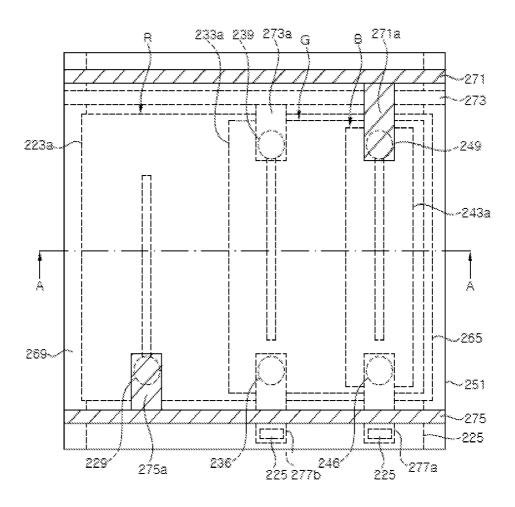

[0063] FIG. 9 is a plan view of a pixel according to an exemplary embodiment.

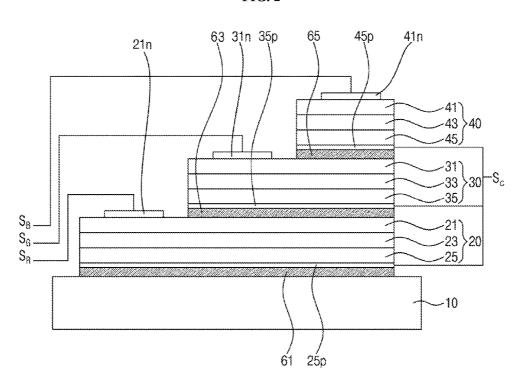

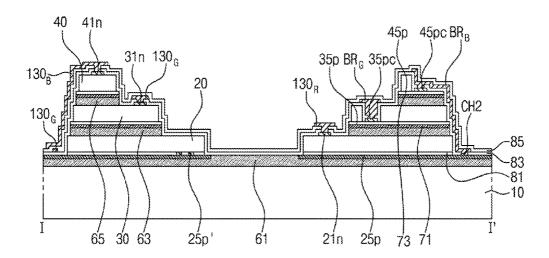

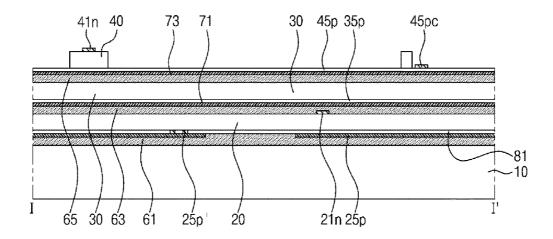

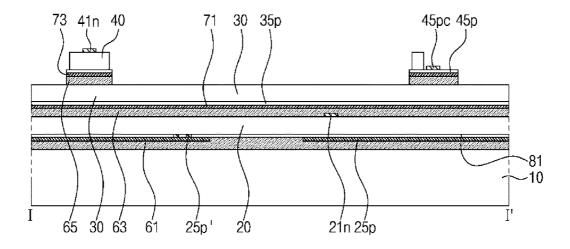

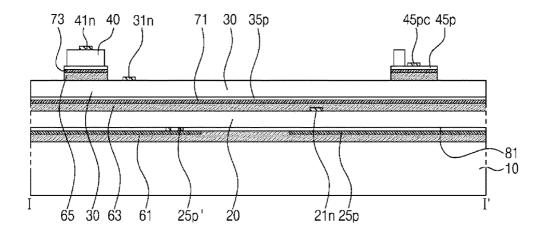

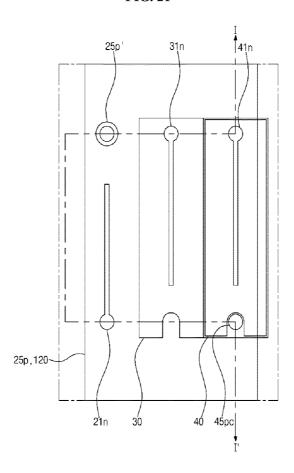

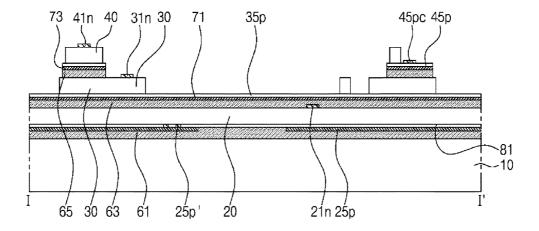

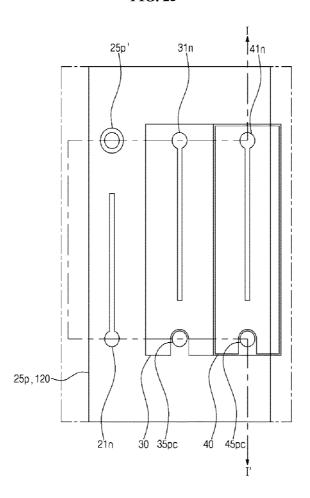

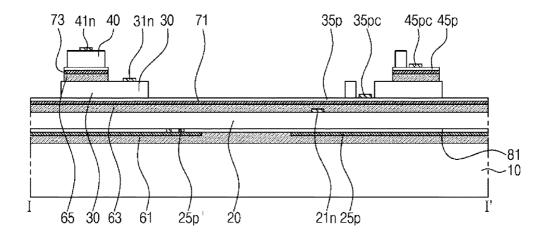

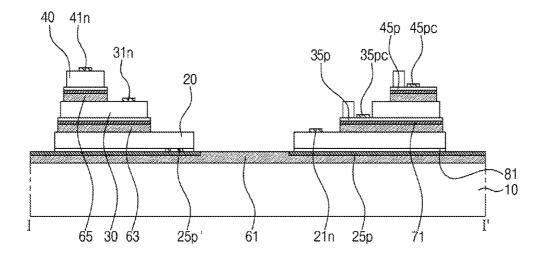

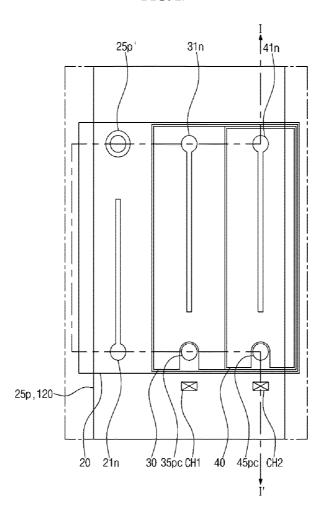

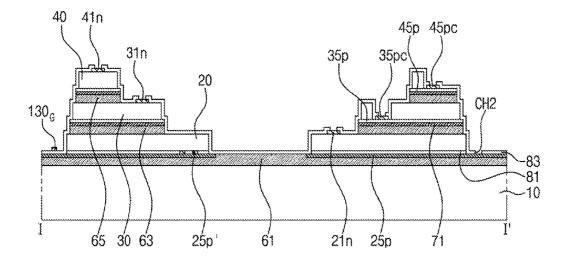

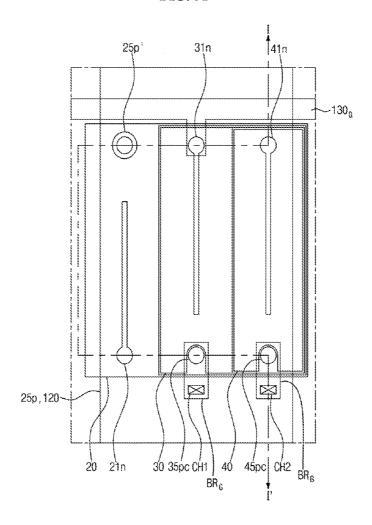

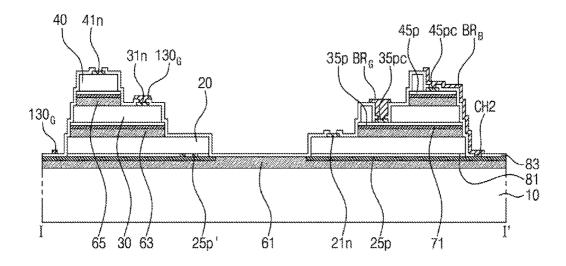

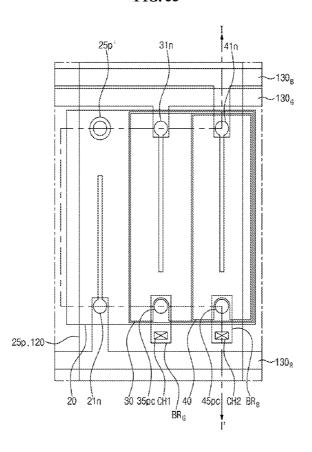

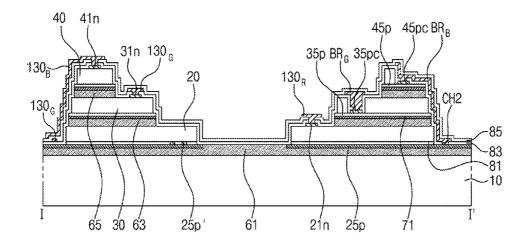

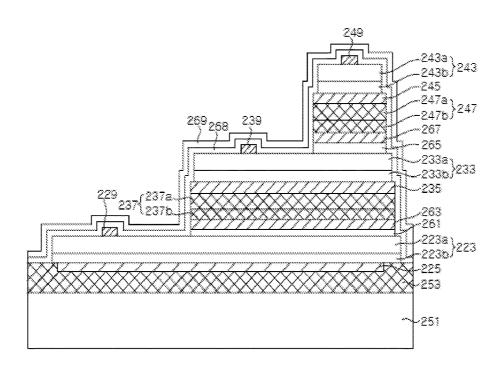

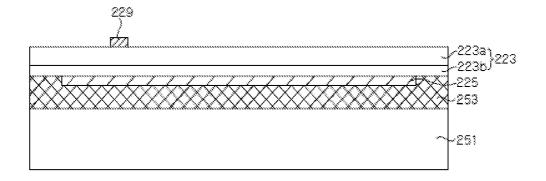

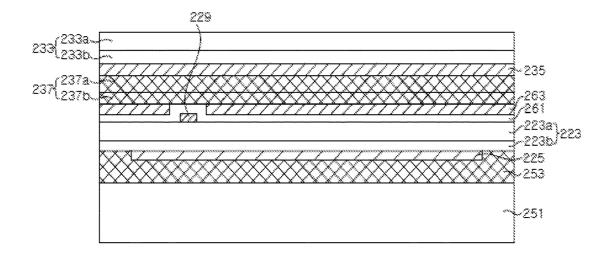

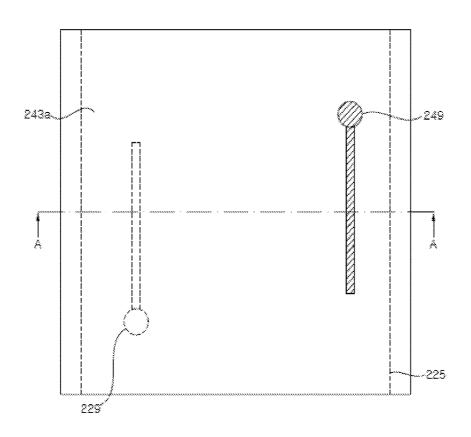

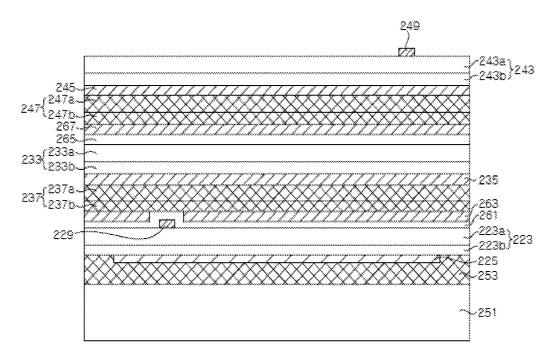

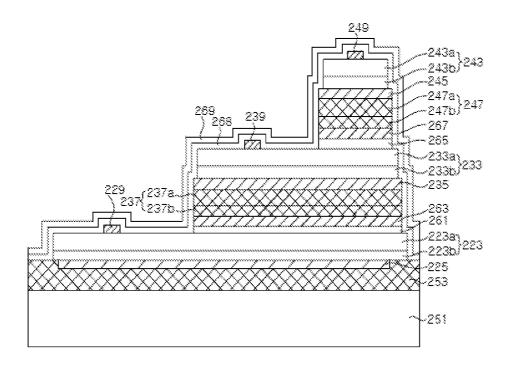

[0064] FIG. 10 is a cross-sectional view taken along line I-I' of FIG. 9.

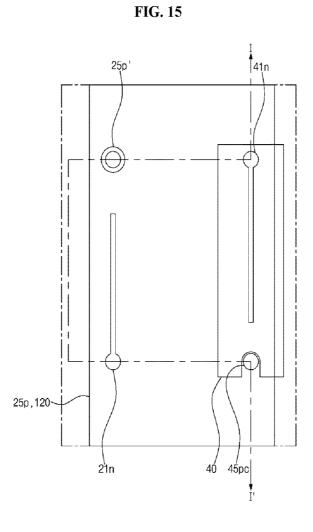

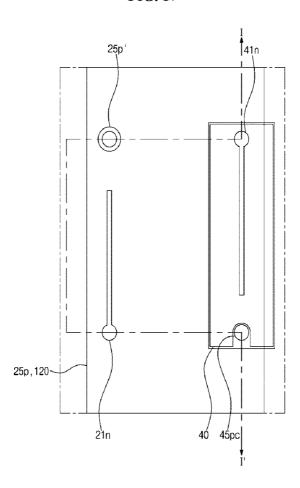

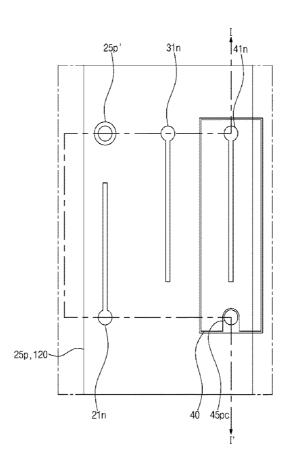

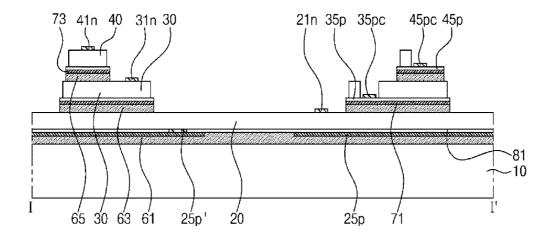

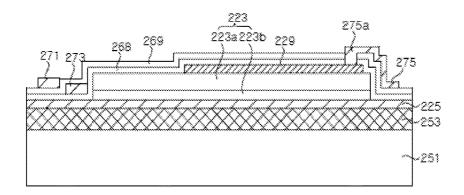

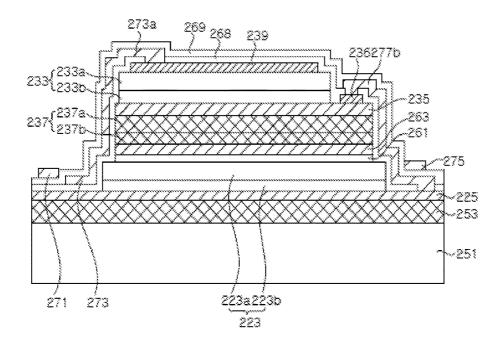

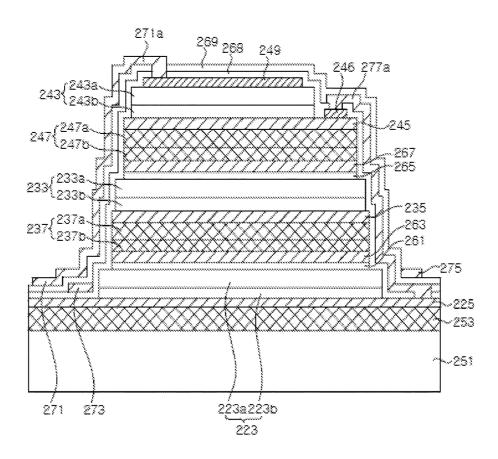

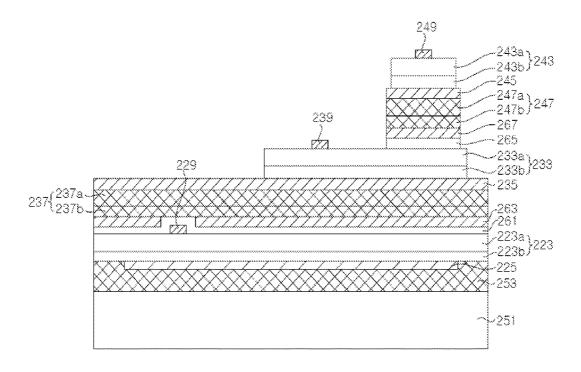

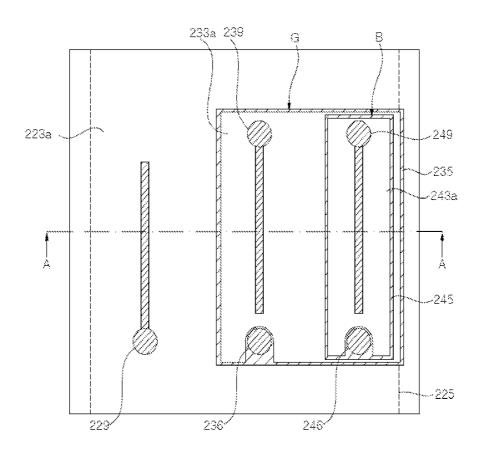

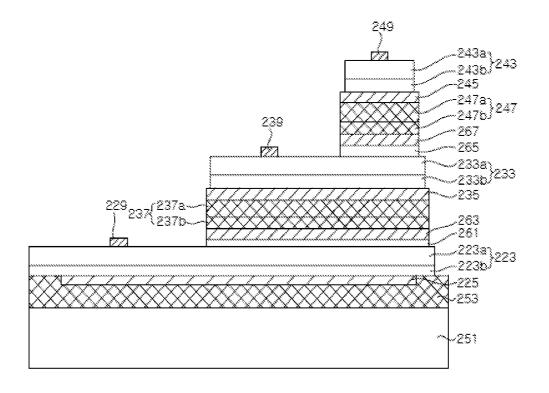

[0065] FIGS. 11, 13, 15, 17, 19, 21, 23, 25, 27, 29, 31, and 33 are plan views illustrating a method of forming first, second, and third epitaxial stacks according to an exemplary embodiment.

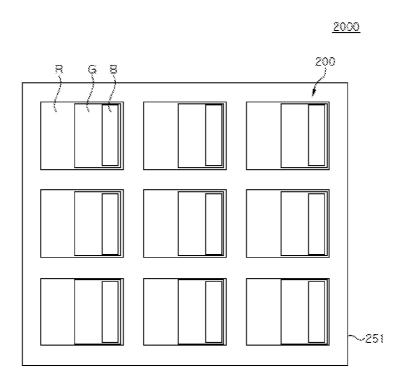

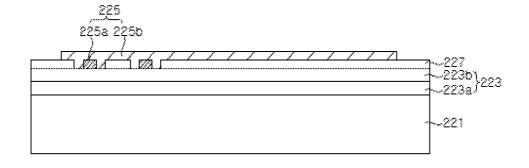

[0066] FIGS. 12, 14, 16, 18, 20, 22, 24, 26, 28, 30, 32, and 34 are cross-sectional views taken along line I-I' of FIGS. 11, 13, 15, 17, 19, 21, 23, 25, 27, 29, 31, and 33, respectively. [0067] FIG. 35 is a schematic plan view of a display apparatus according to an exemplary embodiment.

[0068] FIG. 36 is a schematic cross-sectional view of a light emitting diode pixel for a display according to an exemplary embodiment.

[0069] FIG. 37 is a schematic circuit diagram of a display apparatus according to an exemplary embodiment.

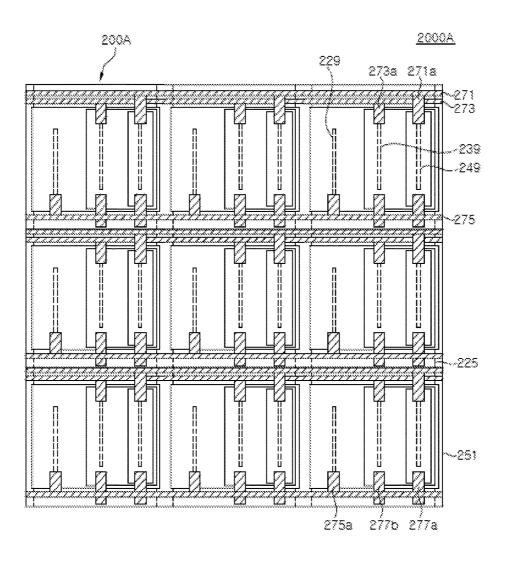

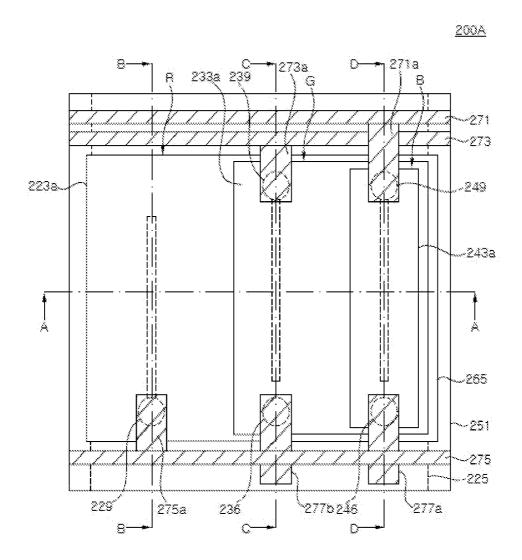

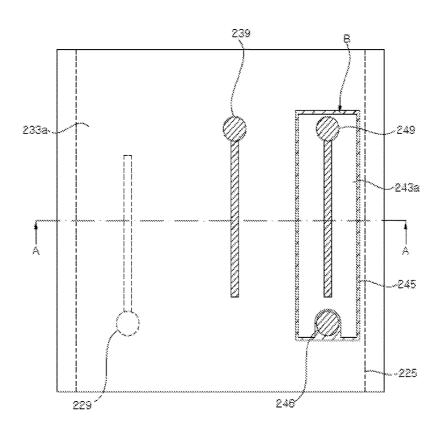

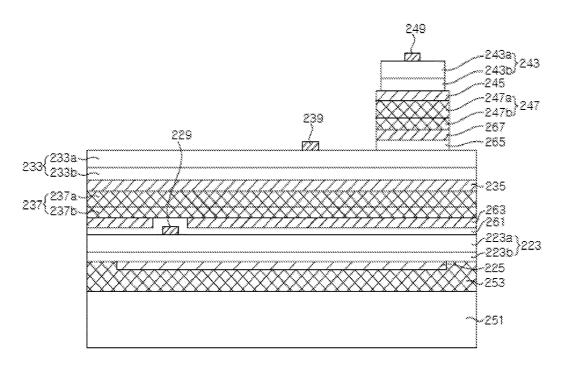

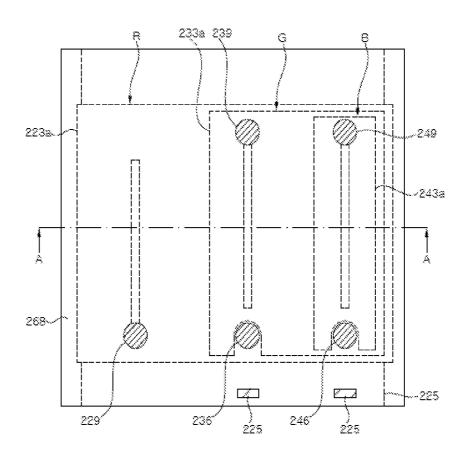

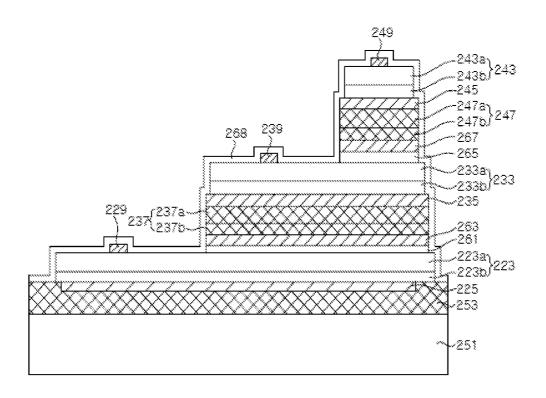

[0070] FIG. 38 is a schematic plan view of a display apparatus according to an exemplary embodiment.

[0071] FIG. 39 is an enlarged plan view of one pixel of the display apparatus of FIG. 38.

[0072] FIG. 40A is a schematic cross-sectional view taken along line A-A of FIG. 39.

[0073] FIG. 40B is a schematic cross-sectional view taken along line B-B of FIG. 39.

[0074] FIG. 40C is a schematic cross-sectional view taken along line C-C of FIG. 39.

[0075] FIG. 40D is a schematic cross-sectional view taken along line D-D of FIG. 39.

[0076] FIGS. 41A, 41B, 41C, 42A, 42B, 43A, 43B, 44A, 44B, 45A, 45B, 46A, 46B, 47A, 47B, 48A, 48B, 49A, 49B, 50A, 50B, 51, 52A, 52B, and 53 are schematic plan view and cross-sectional views illustrating a method of manufacturing a display apparatus according to an exemplary embodiment. [0077] FIG. 54 is a schematic cross-sectional view of a display apparatus according to another exemplary embodiment.

#### DETAILED DESCRIPTION

[0078] In the following description, for the purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of various exemplary embodiments or implementations of the invention. As used herein "embodiments" and "implementations" are interchangeable words that are non-limiting examples of devices or methods employing one or more of the inventive concepts disclosed herein. It is apparent, however, that various exemplary embodiments may be practiced without these specific details or with one or more equivalent arrangements. In other instances, well-known structures and devices are shown in block diagram form in order to avoid unnecessarily obscuring various exemplary embodiments. Further, various exemplary embodiments may be different, but do not have to be exclusive. For example, specific shapes, configurations, and characteristics of an exemplary embodiment may be used or implemented in another exemplary embodiment without departing from the inventive concepts.

[0079] Unless otherwise specified, the illustrated exemplary embodiments are to be understood as providing exemplary features of varying detail of some ways in which the inventive concepts may be implemented in practice. Therefore, unless otherwise specified, the features, components, modules, layers, films, panels, regions, and/or aspects, etc. (hereinafter individually or collectively referred to as "elements"), of the various embodiments may be otherwise combined, separated, interchanged, and/or rearranged without departing from the inventive concepts.

[0080] The use of cross-hatching and/or shading in the accompanying drawings is generally provided to clarify boundaries between adjacent elements. As such, neither the presence nor the absence of cross-hatching or shading conveys or indicates any preference or requirement for particular materials, material properties, dimensions, proportions, commonalities between illustrated elements, and/ or any other characteristic, attribute, property, etc., of the elements, unless specified. Further, in the accompanying drawings, the size and relative sizes of elements may be exaggerated for clarity and/or descriptive purposes. When an exemplary embodiment may be implemented differently, a specific process order may be performed differently from the described order. For example, two consecutively described processes may be performed substantially at the same time or performed in an order opposite to the described order. Also, like reference numerals denote like elements.

[0081] When an element, such as a layer, is referred to as being "on," "connected to," or "coupled to" another element or layer, it may be directly on, connected to, or coupled to the other element or layer or intervening elements or layers may be present. When, however, an element or layer is

referred to as being "directly on," "directly connected to," or "directly coupled to" another element or layer, there are no intervening elements or layers present. To this end, the term "connected" may refer to physical, electrical, and/or fluid connection, with or without intervening elements. Further, the D1-axis, the D2-axis, and the D3-axis are not limited to three axes of a rectangular coordinate system, such as the x, y, and z-axes, and may be interpreted in a broader sense. For example, the D1-axis, the D2-axis, and the D3-axis may be perpendicular to one another, or may represent different directions that are not perpendicular to one another. For the purposes of this disclosure, "at least one of X, Y, and Z" and "at least one selected from the group consisting of X, Y, and Z" may be construed as X only, Y only, Z only, or any combination of two or more of X, Y, and Z, such as, for instance, XYZ, XYY, YZ, and ZZ. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

[0082] Although the terms "first," "second," etc. may be used herein to describe various types of elements, these elements should not be limited by these terms. These terms are used to distinguish one element from another element. Thus, a first element discussed below could be termed a second element without departing from the teachings of the disclosure.

[0083] Spatially relative terms, such as "beneath," "below," "under," "lower," "above," "upper," "over," "higher," "side" (e.g., as in "sidewall"), and the like, may be used herein for descriptive purposes, and, thereby, to describe one elements relationship to another element(s) as illustrated in the drawings. Spatially relative terms are intended to encompass different orientations of an apparatus in use, operation, and/or manufacture in addition to the orientation depicted in the drawings. For example, if the apparatus in the drawings is turned over, elements described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the exemplary term "below" can encompass both an orientation of above and below. Furthermore, the apparatus may be otherwise oriented (e.g., rotated 90 degrees or at other orientations), and, as such, the spatially relative descriptors used herein interpreted accordingly.

[0084] The terminology used herein is for the purpose of describing particular embodiments and is not intended to be limiting. As used herein, the singular forms, "a," "an," and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. Moreover, the terms "comprises," "comprising," "includes," and/or "including," when used in this specification, specify the presence of stated features, integers, steps, operations, elements, components, and/or groups thereof, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. It is also noted that, as used herein, the terms "substantially," "about," and other similar terms, are used as terms of approximation and not as terms of degree, and, as such, are utilized to account for inherent deviations in measured, calculated, and/or provided values that would be recognized by one of ordinary skill in the art.

[0085] Various exemplary embodiments are described herein with reference to sectional and/or exploded illustrations that are schematic illustrations of idealized exemplary embodiments and/or intermediate structures. As such, variations from the shapes of the illustrations as a result, for

example, of manufacturing techniques and/or tolerances, are to be expected. Thus, exemplary embodiments disclosed herein should not necessarily be construed as limited to the particular illustrated shapes of regions, but are to include deviations in shapes that result from, for instance, manufacturing. In this manner, regions illustrated in the drawings may be schematic in nature and the shapes of these regions may not reflect actual shapes of regions of a device and, as such, are not necessarily intended to be limiting.

[0086] Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which this disclosure is a part. Terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning that is consistent with their meaning in the context of the relevant art and should not be interpreted in an idealized or overly formal sense, unless expressly so defined herein.

[0087] Hereinafter, exemplary embodiments of the present disclosure will be explained in detail with reference to the accompanying drawings. As used herein, a light emitting stacked structure or a light emitting diode according to exemplary embodiments may include a micro LED, which has a surface area less than about 10,000 square  $\mu m$  as known in the art. In other exemplary embodiments, the micro LED's may have a surface area of less than about 4,000 square  $\mu m$ , or less than about 2,500 square  $\mu m$ , depending upon the particular application.

[0088] FIG. 1 is a cross-sectional view of a light emitting stacked structure according to an exemplary embodiment.

[0089] Referring to FIG. 1, the light emitting stacked structure according to an exemplary embodiment includes a plurality of epitaxial stacks stacked disposed one over another. The epitaxial stacks are disposed on a substrate 10. The substrate 10 has substantially a plate shape with a front surface and a rear surface.

[0090] The substrate 10 may have various shapes, and the epitaxial stacks may be disposed on a front surface of the substrate 10. The substrate 10 may include an insulating material, such as a glass, a quartz, a silicon, an organic polymer, or an organic-inorganic composite material. However, the inventive concepts are not limited to a particular material of the substrate 10, as long as the substrate 10 has an insulating property. In an exemplary embodiment, a line part may be further disposed on the substrate 10 to apply a light emitting signal and a common voltage to each of the epitaxial stacks. In addition, a driving device including a thin film transistor may further be disposed on the substrate 10, which may drive the epitaxial stacks in an active matrix method. In this case, the substrate 10 may be a printed circuit board or a composite substrate, which may be obtained by forming the line part and/or the driving device on the glass, quartz, silicon, organic polymer, or organic-inorganic composite material, for example.

[0091] The epitaxial stacks are sequentially stacked on the front surface of the substrate 10. In some exemplary embodiments, two or more epitaxial stacks emitting light having different wavelength bands from each other may be disposed. As such, the epitaxial stack may be provided in plural, and the epitaxial stacks may emit light having different energy bands different from each other.

[0092] Each of the epitaxial stacks may have various sizes. In an exemplary embodiment, at least one of the epitaxial stacks may have an area different from the other epitaxial stacks.

[0093] When the epitaxial stacks are sequentially stacked in an upward direction from a lower portion, the area of the epitaxial stacks may become smaller along the upward direction. Among two adjacent epitaxial stacks disposed over one another, at least a portion of the upper epitaxial stack may overlap with the lower epitaxial stack. In some exemplary embodiments, the upper epitaxial stack disposed may completely overlap with the lower epitaxial stack, and in this case, the upper epitaxial stack may be located in an area corresponding to the lower epitaxial stack.

[0094] In the illustrated exemplary embodiment, three epitaxial stacks are sequentially stacked on the substrate 10. The epitaxial stacks disposed on the substrate 10 may include first, second, and third epitaxial stacks 20, 30, and 40.

[0095] The first, second, and third epitaxial stacks 20, 30, and 40 may have different sizes from each other. More particularly, the first, second, and third epitaxial stacks 20, 30, and may have different areas from each other in a plan view, and the first, second, and third epitaxial stacks 20, 30, and 40 may have different widths from each other in a cross-sectional view. In the illustrated exemplary embodiment, the area of the first, second, and third epitaxial stacks 20, 30, and 40 gradually decreases in the order of the first epitaxial stack 20, the second epitaxial stack 30, and the third epitaxial stack 40. The second epitaxial stack 30 is stacked on a portion of the first epitaxial stack 20. Accordingly, a portion of the first epitaxial stack 20 is covered by the second epitaxial stack 30, and the remaining portion of the first epitaxial stack 20 is exposed in a plan view. The third epitaxial stack 40 is stacked on a portion of the second epitaxial stack 30. Accordingly, a portion of the second epitaxial stack 30 is covered by the third epitaxial stack 40, and the remaining portion of the second epitaxial stack 30 is exposed in a plan view.

[0096] The area of the first, second, and third epitaxial stacks 20, 30, and 40 may be changed in various ways. For example, a ratio of area between the first, second, and third epitaxial stacks 20, 30, and 40 may be 3:2:1, however, the inventive concepts are not limited thereto. Each of the first, second, and third epitaxial stacks 20, 30, and 40 may have a different ratio of area in consideration of an amount of light emitted from each epitaxial stack. For example, when the amount of light emitted from the third epitaxial stack 40 is small, the area ratio of the third epitaxial stack 40 may be relatively increased.

[0097] Each of the epitaxial stacks may emit a color light in a visible light band among various wavelength bands. In an exemplary embodiment, light emitted from the lowermost epitaxial stack may have the longest wavelength with the lowest energy band, and the wavelength of the color light emitted from the epitaxial stacks may become shorter from the lowermost to the uppermost epitaxial stacks. For example, light emitted from the uppermost epitaxial stack disposed may have the shortest wavelength with the highest energy band. The first epitaxial stack 20 emits a first color light L1, the second epitaxial stack 30 emits a second color light L2, and the third epitaxial stack 40 emits a third color light L3. The first, second, and third color light L1, L2, and L3 may have different colors from each other, and the first,

second, and third color light L1, L2, and L3 may have different wavelength bands from each other, which are sequentially shortened. In particular, the first, second, and third color light L1, L2, and L3 may have different wavelength bands from each other, which gradually increases from the first color light L1 to the third color light L3.

[0098] In an exemplary embodiment, the first color light L1 may be red light, the second color light L2 may be green light, and the third color light L3 may be blue light. However, the inventive concepts are not limited thereto. When the light emitting stacked structure includes a micro LED, which has a surface area less than about 10,000 square m as known in the art, or less than about 4,000 square m or 2,500 square m in other exemplary embodiments, the first epitaxial stack 20 may emit any one of red, green, and blue light, and the second and third epitaxial stacks 30 and 40 may emit a different one of red, green, and blue light, without adversely affecting operation, due to the small form factor of a micro LED.

[0099] Each epitaxial stack emits light in a direction away from the substrate 10 faces. In this case, light from one epitaxial stack may be emitted directly to the outside in a direction away from the substrate 10, or emitted through an upper epitaxial stack disposed in an optical path. The direction away from the substrate 10 may indicate a direction in which the first, second, and third epitaxial stacks 20, 30, and 40 are stacked. Hereinafter, the direction away from the substrate will be referred to as a "front surface direction" or an "upward direction", and a direction towards the substrate 10 faces will be referred to as a "rear surface direction" or a "downward direction". However, terms "upward" and "downward" are relative terms, which may vary depending on an arrangement or a stacked direction of the light emitting stacked structure.

[0100] Each epitaxial stack emits light towards the upward direction. Light emitted from each epitaxial stack may directly travel in the upward direction or through another epitaxial stack disposed thereabove. In an exemplary embodiment, a first portion of light emitted from the first epitaxial stack 20 directly travels in the upward direction through the exposed upper surface thereof, a second portion of light emitted from the first epitaxial stack 20 travels in the upward direction after passing through the second epitaxial stack 30, and a third portion of the light emitted from the first epitaxial stack 20 travels in the upward direction after passing through the second and third epitaxial stacks 30 and 40. A portion of light emitted from the second epitaxial stack 30 directly travels in the upward direction through the exposed upper surface thereof, and the other portion of the light emitted from the second epitaxial stack 30 travels in the upward direction after passing through the third epitaxial stack 40. Light emitted from the third epitaxial stack 40 directly travels in the upward direction.

[0101] Each epitaxial stack may transmit most of light emitted from the epitaxial stack disposed thereunder. In particular, the portion of light emitted from the first epitaxial stack 20 travels in the front surface direction after passing through the second epitaxial stack 30 and the third epitaxial stack 40, and the portion of light emitted from the second epitaxial stack 30 travels in the front surface direction after passing through the third epitaxial stack 40. As such, at least a portion or an entire portion of other epitaxial stacks except for the lowermost epitaxial stack may be formed of a light transmitting material. As used herein, the term "light trans-

mitting material" may refer to a material transmitting an entire light or a material transmitting a predetermined wavelength or a portion of light having a predetermined wavelength. In an exemplary embodiment, each epitaxial stack may transmit about 60% or more of light emitted from the epitaxial stack disposed thereunder. According to another exemplary embodiment, each epitaxial stack may transmit about 80% or more of light from the epitaxial stack disposed thereunder, and according to another exemplary embodiment, each epitaxial stack may transmit about 90% or more of light from the epitaxial stack disposed thereunder.

[0102] According to an exemplary embodiment, the epitaxial stacks may be independently driven as signal lines that respectively apply light emitting signals to the epitaxial stacks are independently connected to the epitaxial stacks, and thus, may display various colors depending on whether light is emitted from each epitaxial stack. In addition, since the epitaxial stacks emitting light having difference wavelengths are formed to be overlapped with each other, the light emitting stacked structure may be formed in a narrow area.

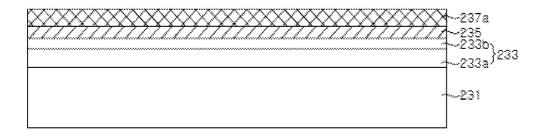

[0103] FIG. 2 is a cross-sectional view of a light emitting stacked structure an exemplary embodiment.

[0104] Referring to FIG. 2, the light emitting stacked structure according to an exemplary embodiment includes the first, second, and third epitaxial stacks 20, 30, and 40 disposed on the substrate 10, with first, second, and third adhesive layers 61, 63, and 65 therebetween. The first adhesive layer 61 may include a conductive or non-conductive material. In some exemplary embodiments, the first adhesive layer 61 may have a conductivity at portions thereof to be electrically connected to the substrate 10 disposed thereunder. The first adhesive layer 61 may include a transparent or non-transparent material. When the substrate 10 includes the non-transparent material and the line part is formed on the substrate 10, the first adhesive layer 61 may include the non-transparent material, for example, a light absorbing material, such as an epoxy-based polymer adhesive.

[0105] The second and third adhesive layers 63 and 65 may include a non-conductive material and may include a light transmitting material. For example, the second and third adhesive layers 63 and 65 may include an optically clear adhesive (OCA). However, the inventive concepts are not limited to a particular material of the second and third adhesive layers 63 and 65, as long as the second and third adhesive layers 63 and 65 are optically clear and stably attach each epitaxial stack. For example, the second and third adhesive layers 63 and 65 may include an organic material, such as an epoxy-based polymer like SU-8, various resists, parylene, poly(methyl methacrylate) (PMMA), benzocyclobutene (BCB), and spin on glass (SOG), and an inorganic material, such as silicon oxide and aluminum oxide. In some exemplary embodiments, a conductive oxide may be used as the adhesive layer, and in this case, the conductive oxide may be insulated from other components. When the organic material is used as the adhesive layer, the first, second, and third epitaxial stacks 20, 30, and 40 and the substrate 10 may be attached to each other by coating the material on an adhesive side of the first, second, and third epitaxial stacks 20, 30, and 40 and the substrate 10, and applying a high temperature and a high pressure to the material under a high vacuum state. When the inorganic material is used as the adhesive layer, the first, second, and third epitaxial stacks 20, 30, and 40 and the substrate 10 may be attached to each other by depositing the material on the adhesive side of the first, second, and third epitaxial stacks 20, 30, and 40 and the substrate 10, planarizing the material using a chemical-mechanical planarization (CMP), performing a plasma treatment on a surface of the material, and attaching under the high vacuum state, for example. Each of the first, second, and third epitaxial stacks 20, 30, and 40 includes a p-type semiconductor layer 25, 35, and 45, an active layer 23, 33, and 43, and an n-type semiconductor layer 21, 31, and 41, which are sequentially stacked.

[0106] The p-type semiconductor layer 25, the active layer 23, and the n-type semiconductor layer 21 of the first epitaxial stack 20 may include a semiconductor material that emits red light, such as aluminum gallium arsenide (Al-GaAs), gallium arsenide phosphide (GaAsP), aluminum gallium indium phosphide (Al-GalnP), and gallium phosphide (GaP), etc., without being limited thereto.

[0107] A first p-type contact electrode layer 25p may be disposed under the p-type semiconductor layer 25 of the first epitaxial stack 20. The first p-type contact electrode layer 25p of the first epitaxial stack 20 may have a single-layer structure or a multi-layer structure and may include metal. For example, the first p-type contact electrode layer 25p may include metal, such as Al, Ti, Cr, Ni, Au, Ag, Sn, W, Cu, or an alloy thereof. The first p-type contact electrode layer 25p may include metal having high reflectance to improve light emission efficiency in the upward direction by the reflecting light emitted from the first epitaxial stack 20.

[0108] A first n-type contact electrode 21n may be disposed on the n-type semiconductor layer of the first epitaxial stack 20. The first n-type contact electrode 21n of the first epitaxial stack 20 may have a single-layer structure or a multi-layer structure and may include metal. For example, the first n-type contact electrode 21n may include metal, such as Al, Ti, Cr, Ni, Au, Ag, Sn, W, Cu, or an alloy thereof. However, the inventive concepts are not limited thereto, and other conductive materials may be used.

[0109] The second epitaxial stack 30 includes the p-type semiconductor layer 35, the active layer 33, and the n-type semiconductor layer 31, which are sequentially stacked. The p-type semiconductor layer 35, the active layer 33, and the n-type semiconductor layer 31 may include a semiconductor material that may emit green light, such as indium gallium nitride (InGaN), gallium nitride (GaN), gallium phosphide (GaP), aluminum gallium indium phosphide (AlGaInP), and aluminum gallium phosphide (AlGaP), for example, without being limited thereto.

[0110] A second p-type contact electrode layer 35p is disposed under the p-type semiconductor layer 35 of the second epitaxial stack 30. The second p-type contact electrode layer 35p is disposed between the first epitaxial stack 20 and the second epitaxial stack 30, in detail, between the second adhesive layer 63 and the second epitaxial stack 30.

[0111] A second n-type contact electrode 3 in may be disposed on the n-type semiconductor layer of the second epitaxial stack 30. The second n-type contact electrode 3 in of the second epitaxial stack 30 may have a single-layer structure or a multi-layer structure, and may include metal. For example, the second n-type contact electrode 31n may include metal, such as Al, Ti, Cr, Ni, Au, Ag, Sn, W, Cu, or an alloy thereof. However, the inventive concepts are not limited thereto, and other conductive materials may be used.

[0112] The third epitaxial stack 40 includes the p-type semiconductor layer 45, the active layer 43, and the n-type semiconductor layer 41, which are sequentially stacked. The p-type semiconductor layer 45, the active layer 43, and the n-type semiconductor layer 41 may include a semiconductor material that may emit blue light, such as gallium nitride (GaN), indium gallium nitride (InGaN), and zinc selenide (ZnSe), for example, without being limited thereto.

[0113] A third p-type contact electrode layer 45p is disposed under the p-type semiconductor layer 45 of the third epitaxial stack 40. The third p-type contact electrode layer 45p is disposed between the second epitaxial stack 30 and the third epitaxial stack 40, in detail, between the third adhesive layer 65 and the third epitaxial stack 40.

[0114] A third n-type contact electrode 41n may be disposed on the n-type semiconductor layer of the third epitaxial stack 40. The third n-type contact electrode 41n of the third epitaxial stack 40 may have a single-layer structure or a multi-layer structure, and may include metal. For example, the third n-type contact electrode 41n may include metal, such as Al, Ti, Cr, Ni, Au, Ag, Sn, W, Cu, or an alloy thereof. However, the inventive concepts are not limited thereto, and other conductive materials may be used.

[0115] FIG. 2 shows that each of the n-type semiconductor layers 21, 31, and 41 and each of the p-type semiconductor layer 25, 35, and 45 of the first, second, and third epitaxial stacks 20, 30, and 40 has the single-layer structure, however, in some exemplary embodiments, these layers may have a multi-layer structure and may include a superlattice layer. The active layers 23, 33, and 43 of the first, second, and third epitaxial stacks 20, 30, and 40 may have a single quantum well structure or a multiple quantum well structure.

[0116] The second p-type contact electrode layer 35p may have an area that substantially covers the second epitaxial stack 30. In addition, the third p-type contact electrode layer **45**p may have an area that substantially covers the third epitaxial stack 40. In this case, the second and third p-type contact electrode layers 35p and 45p may include a transparent conductive material to transmit light emitted from the epitaxial stack disposed thereunder. For example, each of the second and third p-type contact electrode layers 35p and 45p may include the transparent conductive oxide (TCO), which may include tin oxide (SnO), indium oxide (InO<sub>2</sub>), zinc oxide (ZnO), indium tin oxide (ITO), and indium tin zinc oxide (ITZO). The transparent conductive compound may be deposited by a chemical vapor deposition (CVD) or a physical vapor deposition (PVD) using an evaporator or a sputter, for example. The second and third p-type contact electrode layers 35p and 45p may have a thickness, e.g., from about 2000 angstroms to about 2 micrometers, so as to function as an etch stopper in the following manufacturing process while having a predetermined light transmittance.

[0117] In an exemplary embodiment, the first, second, and third p-type contact electrode layers 25p, 35p, and 45p may be connected to a common line. The common line is a line to which the common voltage is applied. In addition, light emitting signal lines may be respectively connected to the first, second, and third n-type contact electrodes 21n, 31n, and 41n. In an exemplary embodiment, the common voltage Sc is applied to the first p-type contact electrode layer 25p, the second p-type contact electrode layer 35p, and the third p-type contact electrode layer 45p through the common line, and the light emitting signal is applied to the first, second, and third n-type contact electrodes 21n, 31n, and 41n

through the light emitting signal lines. Accordingly, the first, second, and third epitaxial stacks **20**, **30**, and **40** may be independently controlled. The light emitting signal includes first, second, and third light emitting signals  $S_R$ ,  $S_G$ , and  $S_B$  respectively corresponding to the first, second, and third epitaxial stacks **20**, **30**, and **40**. In an exemplary embodiment, the first, second, and third light emitting signals  $S_R$ ,  $S_G$ , and  $S_B$  are signals respectively corresponding to light emissions of red light, green light, and blue light.

[0118] In the illustrated exemplary embodiment, the common voltage is applied to the p-type semiconductor layers 25, 35, and 45 of the first, second, and third epitaxial stacks 20, 30, and 40, and the light emitting signal is applied to the n-type semiconductor layers 21, 31, and 41 of the first, second, and third epitaxial stacks 20, 30, and 40, however, the inventive concepts are not limited thereto. For example, in some exemplary embodiments, the common voltage may be applied to the n-type semiconductor layers 21, 31, and 41 of the first, second, and third epitaxial stacks 20, 30, and 40, and the light emitting signal may be applied to the p-type semiconductor layers 25, 35, and 45 of the first, second, and third epitaxial stacks 20, 30, and 40.

[0119] The first, second, and third epitaxial stacks 20, 30, and 40 may be driven in response to the light emitting signal applied thereto. More particularly, the first epitaxial stack 20 is driven in response to the first light emitting signal  $S_R$ , the second epitaxial stack 30 is driven in response to the second light emitting signal  $S_G$ , and the third epitaxial stack 40 is driven in response to the third light emitting signal  $S_B$ . In this case, the first, second and third light emitting signals  $S_R$ ,  $S_G$ , and  $S_B$  are independently applied to the first, second, and third epitaxial stacks 20, 30, and 40, and thus, the first, second, and third epitaxial stacks 20, 30, and 40 are independently driven. The light emitting stacked structure may provide light having various colors by a combination of the first, second, and third color light emitted from the first, second, and third epitaxial stacks 20, 30, and 40 to the upward direction.

[0120] The light emitting stacked structure having the above-described structure according to exemplary embodiments may have an improved light extraction efficiency as compared to a structure having the epitaxial stacks completely overlap with each other. In particular, the amount of light emitted from the first, second, and third epitaxial stacks 20, 30, and 40 in the upper direction without passing through other epitaxial stacks may be increased, which may improve the light extraction efficiency.

[0121] In addition, the light emitting stacked structure according to exemplary embodiments may display various colors by a combination of different colors of light emitted to from overlapping epitaxial stacks, rather than providing different color lights through different areas spaced apart from each other on a plane, and thus, a light emitting element according to exemplary embodiments may have a reduced size with increased integration. A conventional light emitting elements that emit different colors of light, e.g., red, green, and blue lights, are spaced apart from each other on a plane to implement a full color display. Accordingly, an area occupied by the conventional light emitting elements is relatively large since the light emitting elements are spaced apart from each other on the plane. However, light emitting elements according to exemplary embodiments that emit the different colors of light are disposed in the same area while being overlapped with each other to form the light emitting

stacked structure, and thus, the full color display may be implemented through a significantly smaller area than that of the conventional art. Therefore, a high-resolution display device may be manufactured in a small area.

[0122] Further, even when a conventional light emitting device is manufactured in a stacked manner, the conventional light emitting device is manufactured by individually forming a contact part in each light emitting element, e.g., by forming light emitting elements individually and separately and connecting the light emitting elements to each other using a wiring, which may increase the structural complexity and manufacturing complexity. However, the light emitting stacked structure according to the exemplary embodiments may be manufactured by sequentially stacking plural epitaxial stacks on one substrate, forming the contact part in the epitaxial stacks through a simplified process, and connecting the line part to the epitaxial stacks. In addition, since one light emitting stacked structure is mounted according to exemplary embodiments, the manufacturing method of the display device may be significantly simplified compared with the conventional display device manufacturing method, which may separately manufacture the light emitting elements of individual colors and individually mounting the light emitting elements.

[0123] The light emitting stacked structure according the exemplary embodiments may further include various components to provide high purity color light and high efficiency. For example, the light emitting stacked structure may include a wavelength pass filter to prevent light having a relatively shorter wavelength from traveling towards the epitaxial stack emitting light having a relatively longer wavelength.

[0124] Hereinafter, different features and elements from those described above will be mainly described in order to avoid redundancy. As such, detailed descriptions of the substantially the same elements will be omitted to avoid redundancy.

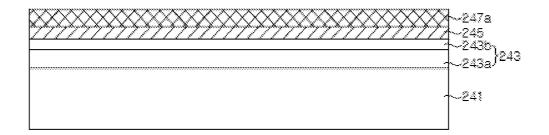

[0125] FIG. 3 is a cross-sectional of a light emitting stacked structure according to an exemplary embodiment.

[0126] Referring to FIG. 3, the light emitting stacked structure may include a first wavelength pass filter 71 disposed between the first epitaxial stack 20 and the second epitaxial stack 30.

[0127] The first wavelength pass filter 71 may selectively transmit light having a predetermined wavelength. The first wavelength pass filter 71 may transmit the first color light emitted from the first epitaxial stack 20 and may block or reflect light except for the first color light. Accordingly, the first color light emitted from the first epitaxial stack 20 may travel in the upward direction, but the second and third color light respectively emitted from the second and third epitaxial stacks 30 and 40 may not travel toward the first epitaxial stack 20 and may be reflected or blocked by the first wavelength pass filter 71.

[0128] The second and third color light may have relatively shorter wavelength and relatively higher energy than the first color light. When the second and third color lights are incident into the first epitaxial stack 20, a secondary light emission may be induced in the first epitaxial stack 20. According to an exemplary embodiment, however, the second and third color lights may be prevented from being incident into the first epitaxial stack 20 by the first wavelength pass filter 71.

[0129] In an exemplary embodiment, a second wavelength pass filter 73 may be disposed between the second epitaxial stack 30 and the third epitaxial stack 40. The second wavelength pass filter 73 may transmit the first and second color lights respectively emitted from the first and second epitaxial stacks 20 and 30, and may block or reflect light except for the first and second color lights. Accordingly, the first and second epitaxial stacks 20 and 30 may travel in the upward direction, but the third color light emitted from the third epitaxial stack 40 may not travel toward the first and second epitaxial stacks 20 and 30, and may be reflected or blocked by the second wavelength pass filter 73.

[0130] The third color light has relatively shorter wavelength and relatively higher energy than the first and second color lights. When the third color light is incident into the first and second epitaxial stacks 20 and 30, a secondary light emission may be induced in the first and second epitaxial stacks 20 and 30. According to an exemplary embodiment, however, the third color light may be prevented from being incident into the first and second epitaxial stacks 20 and by the second wavelength pass filter 73.

[0131] The first and second wavelength pass filters 71 and 73 may be formed in various ways. For example, the first and second wavelength pass filters 71 and 73 may be formed by alternately stacking insulating layers having different refractive indices from each other. For example, silicon dioxide ( $\mathrm{SiO}_2$ ) and titanium dioxide ( $\mathrm{TiO}_2$ ) may be alternately stacked on each other, and a wavelength of light may be determined by adjusting a thickness and/or the number of stacked layers of each of the silicon dioxide ( $\mathrm{SiO}_2$ ) and the titanium dioxide ( $\mathrm{TiO}_2$ ). In some exemplary embodiments,  $\mathrm{SiO}_2$ ,  $\mathrm{TiO}_2$ ,  $\mathrm{HfO}_2$ ,  $\mathrm{Nb20}_5$ ,  $\mathrm{ZrO}_2$ , and  $\mathrm{Ta_2O}_5$  may be used as the insulating layers having different refractive indices.

[0132] The light emitting stacked structure according to an exemplary embodiment may further include various components to provide high efficiency uniform light. For example, various concave-convex portions may be formed on a light emitting surface. In some exemplary embodiments, the concave-convex portions may formed on the n-type semiconductor layer of at least one of the first, second, and third epitaxial stacks 20, 30, and 40, which may be a light emitting surface.

[0133] The concave-convex portion may improve a light emitting efficiency. The concavo-convex portion may be provided in various shapes, such as a polygonal pyramid, a hemisphere, or a surface having a roughness, on which concavo-convex portions are randomly arranged. The concave-convex portion may be textured through various etching processes or may be formed using a patterned sapphire substrate.

[0134] The first, second, and third color lights emitted from the first, second, and third epitaxial stacks 20, 30, and 40 may have difference intensities, and the intensity difference may cause a difference in visibility. In an exemplary embodiment, the light emitting efficiency may be improved by forming the concave-convex portion selectively on the light emitting surfaces of the first, second, and third epitaxial stacks 20, 30, and 40, to reduce the difference in visibility between the first, second, and third color lights. Since the color light corresponding to the red and/or blue colors has lower visibility than color light corresponding to green color, the difference in visibility may be reduced by texturing the first epitaxial stack 20 and/or the third epitaxial stack

**40**. In particular, the red color light has a relatively smaller intensity as the red color light may be provided from the lowermost portion of the light emitting stacked structure. In this case, when the concave-convex portion is formed on the first epitaxial stack **20** to improve light efficiency thereof.

[0135] The light emitting stacked structure having the above-described structure may correspond to a light emitting element capable of displaying various colors, and may be employed in a display device as a pixel. Hereinafter, a display device including the light emitting stacked structure according to exemplary embodiments will be described in more detail.

[0136] FIG. 4 is a plan view of a display device according to an exemplary embodiment, and FIG. 5 is an enlarged plan view of portion P1 of FIG. 4.

[0137] Referring to FIGS. 4 and 5, the display device 100 according to an exemplary embodiment may display any visual information, such as a text, a video, a photograph, and a 2D or 3D image.

[0138] The display device 100 may have various shapes, such as a closed polygonal shape with straight sides, a circular or oval shape with a curved side, and a semi-circular or semi-oval shape with a straight side and a curved side. In the illustrated exemplary embodiment, the display device 100 will be described as having substantially a rectangular shape.

[0139] The display device 100 includes a plurality of pixels 110 that display an image. Each pixel 110 may be a minimum unit that displays the image. Each pixel 110 may include the light emitting stacked structure according to an exemplary embodiment and may emit a white light and/or a color light.

[0140] Each pixel 110 according to an exemplary embodiment includes a first pixel  $110_R$  emitting red color light, a second pixel  $110_G$  emitting green color light, and a third pixel  $110_B$  emitting blue color light. The first, second, and third pixels  $110_R$ ,  $110_G$ , and  $110_B$  may respectively correspond to the first, second, and third epitaxial stacks 20, 30, and 40 of the light emitting stacked structure described above.

[0141] The pixels 110 are arranged in a matrix form. As used herein, the pixels 110 being arranged in the matrix form may refer to that the pixels 110 are arranged exactly in line along rows or columns, as well as the pixels 110 being arranged substantially along the rows or columns, while detailed locations of the pixels 110 may be varied, e.g., a zigzag form.

[0142] FIG. 6 is a block diagram of a display device according to an exemplary embodiment.

[0143] Referring to FIG. 6, the display device 100 according to an exemplary embodiment includes a timing controller 350, a scan driver 310, a data driver 330, a line part, and the pixels. Each of the pixels is individually connected to the scan driver 310 and the data driver 330 through the line part.

[0144] The timing controller 350 receives various control signals and image data, which may be used to drive the display device 100, from an external source (e.g., an external system that transmits the image data). The timing controller 350 may rearrange the received image data and apply the rearranged image data to the data driver 330. In addition, the timing controller 350 may generate scan control signals and data control signals, which may be used to drive the scan driver 310 and the data driver 330, and apply the generated

scan control signals and the data control signals to the scan driver 310 and the data driver 330, respectively.

[0145] The scan driver 310 may receive the scan control signals from the timing controller 350 and generate scan signals in response to the scan control signals.

[0146] The data driver 330 may receive the data control signals and the image data from the timing controller 350 and generate data signals in response to the data control signals.

[0147] The line part includes a plurality of signal lines. In particular, the line part includes scan lines  $130_R$ ,  $130_G$ , and  $130_B$  (hereinafter, collectively indicated as "130") that connect the scan driver 310 to the pixels, and data lines 120 that connect the data driver 330 to the pixels. The scan lines 130 may be connected to the pixels, respectively, and the scan lines respectively connected to the pixels are shown in first, second and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$ .

[0148] In addition, the line part may further include lines that connect the timing controller 350 and the scan driver 310, the timing controller 350 and the data driver 330, or other components to each other to transmit signals.

[0149] The scan lines 130 apply the scan signals generated by the scan driver 310 to the pixels. The data signals generated by the data driver 330 are applied to the data lines 120.

[0150] The pixels are connected to the scan lines 130 and the data lines 120. The pixels may selectively emit light in response to the data signals provided from the data lines 120 when the scan signals from the scan lines 103 are applied thereto. For example, each of the pixels may emit light having the brightness that corresponds to the data signal applied thereto during each frame period. The pixels, to which the data signals corresponding to a black brightness are applied, may not emit light during corresponding frame period, and thus, displaying a black color.

[0151] In an exemplary embodiment, the pixels may be driven in a passive or an active matrix manner. When the display device is driven in the active matrix manner, the display device 100 may be further supplied with first and second pixel power sources, in addition to the scan signals and the data signals.

[0152] FIG. 7 is a circuit diagram of one pixel for a passive matrix type display device according to an exemplary embodiment. The pixel may be one of the pixels, e.g., the red pixel, the green pixel, and the blue pixel, and the pixel will be described with reference to the first pixel  $110_R$ . The second and third pixels may be driven in substantially the same manner as the first pixel, and thus, detailed descriptions of circuit diagrams of the second and third pixels will be omitted to avoid redundancy.

[0153] Referring to FIG. 7, the first pixel  $\mathbf{110}_R$  includes a light emitting element  $\mathbf{150}$  connected between the first scan line  $\mathbf{130}_R$  and the data line  $\mathbf{120}$ . The light emitting element  $\mathbf{150}$  may correspond to the first epitaxial stack  $\mathbf{20}$ . When a voltage equal to or greater than a threshold voltage is applied to between the p-type semiconductor layer and the n-type semiconductor layer, the first epitaxial stack  $\mathbf{20}$  emits light having the brightness that corresponds to a level of the voltage applied thereto. As such, the light emission of the first pixel  $\mathbf{110}_R$  may be controlled by controlling a voltage of the scan signal applied to the first scan line  $\mathbf{130}_R$  and/or a voltage of the data signal applied to the data line  $\mathbf{120}$ .

[0154] FIG. 8 is a circuit diagram of one pixel for an active matrix type display device according to an exemplary embodiment.

[0155] When the display device is the active matrix type display device, the first pixel  $110_R$  may be further supplied with first and second pixel power sources ELVDD and ELVSS, in addition to the scan signals and the data signals. [0156] Referring to FIG. 8, the first pixel  $110_R$  includes one or more light emitting elements 150 and a transistor part connected to the light emitting element 150.

[0157] The light emitting element 150 may correspond to the first epitaxial stack 20, the p-type semiconductor layer of the light emitting element 150 may be connected to the first pixel power source ELVDD via the transistor part, and the n-type semiconductor layer of the light emitting element 150 may be connected to the second pixel power source ELVSS. The first pixel power source ELVDD and the second pixel power source ELVSS may have different electric potentials from each other. For example, the second pixel power source ELVSS may have an electric potential lower than an electric potential of the first pixel power source ELVDD by at least the threshold voltage of the light emitting element. Each of the light emitting elements may emit light having a brightness that corresponds to a driving current controlled by the transistor part.

[0158] The transistor part according to an exemplary embodiment includes first and second transistors M1 and M2 and a storage capacitor Cst. However, a configuration of the transistor part may be variously modified.

[0159] The first transistor M1 (switching transistor) includes a source electrode connected to the data line 120, a drain electrode connected to a first node N1, and a gate electrode connected to the first scan line  $130_R$ . The first transistor M1 is turned on to electrically connect the data line 120 and the first node N1 when the scan signal having the voltage sufficient to turn on the first transistor M1 is provided through the first scan line  $130_R$ . In this case, the data signal of the corresponding frame is applied to the data line 120, and thus, the data signal is applied to the first node N1. The storage capacitor Cst is charged with the data signal applied to the first node N1.

[0160] The second transistor M2 (driving transistor) includes a source electrode connected to the first pixel power source ELVDD, a drain electrode connected to the n-type semiconductor layer of the light emitting element 150, and a gate electrode connected to the first node N1. The second transistor M2 controls an amount of the driving current supplied to the light emitting element 150 in response to the voltage of the first node N1.

[0161] One electrode of the storage capacitor Cst is connected to the first pixel power source ELVDD, and the other electrode of the storage capacitor Cst is connected to the first node N1. The storage capacitor Cst is charged with the voltage corresponding to the data signal applied to the first node N1 and maintains the charged voltage until a data signal of a next frame is provided.

[0162] In the illustrated exemplary embodiment, the transistor part is described as including two transistors as shown in FIG. 8. However, the inventive concepts are not limited to a particular number of the transistors included in the transistor part, and the configuration of the transistor part may be changed in various ways. For example, the transistor part may include more transistors and more capacitors. In addition, the configurations of the first and second transis-

tors, the storage capacitor, and the lines are well known in the art, and thus, detailed descriptions thereof will be omitted. In some exemplary embodiments, the configurations of the first and second transistors, the storage capacitor, and the lines may be changed in various ways. Hereinafter, the pixel will be described with reference to a passive matrix-type pixel.

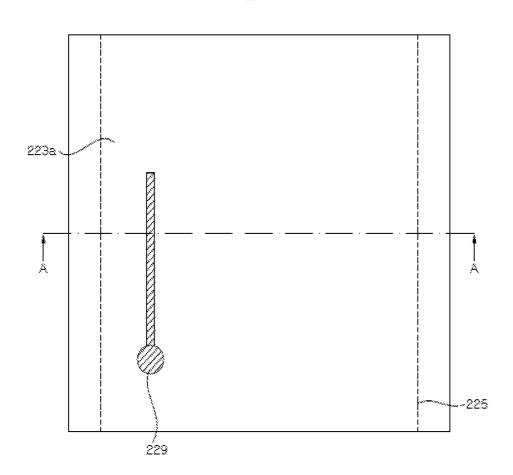

[0163] FIG. 9 is a plan view of a pixel according to an exemplary embodiment, and FIG. is a cross-sectional view taken along line I-I of FIG. 9.

[0164] Referring to FIGS. 9 and 10, the pixel according to an exemplary embodiment includes a plurality of epitaxial stacks stacked one above another, and the epitaxial stacks include the first, second, and third epitaxial stacks 20, 30, and 40.

[0165] The first epitaxial stack 20 may have the largest area among the epitaxial stacks. The second epitaxial stack 30 has an area smaller than that of the first epitaxial stack 20 and is disposed on a portion of the first epitaxial stack 20. The third epitaxial stack 40 has an area smaller than that of the second epitaxial stack 30 and is disposed on a portion of the second epitaxial stack 30. In the illustrated exemplary embodiment, the first, second, and third epitaxial stacks 20, 30, and 40 are arranged such that upper surfaces of the first, second, and third epitaxial stacks 20, 30, and 40 are sequentially exposed.

[0166] The contact part is disposed in the pixel to connect the line part to the first, second, and third epitaxial stacks 20, 30, and 40. In some exemplary embodiments, the stacked structure of a pixel may be changed depending on to which polarity type semiconductor layers of the first, second, and third epitaxial stacks 20, 30, and 40 the common voltage is applied. Hereinafter, the common voltage will be described as being applied to the p-type semiconductor layer of the first, second, and third epitaxial stacks 20, 30, and 40, as an example.

[0167] The first, second, and third light emitting signal lines that respectively apply the light emitting signals to the first, second, and third epitaxial stacks 20, 30, and 40, and the common line that applies the common voltage to each of the first, second, and third epitaxial stacks 20, 30, and 40 are connected to the first, second, and third epitaxial stacks 20, 30, and 40. The first, second, and third light emitting signal lines may respectively correspond to the first, second, and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$ , and the common line may correspond to the data line 120, and thus, the first, second, and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$  and the data line 120 are connected to the first, second, and third epitaxial stacks 20, 30, and 40.

[0168] The first, second, and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$  according to an exemplary embodiment may extend in a first direction, e.g., a horizontal direction of FIG. 9. The data line 120 may extend in a second direction, e.g., a vertical direction of FIG. 9, that crosses the first, second, and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$ . However, the directions in which the first, second, and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$  and the data line 120 extend are not limited thereto, and may be changed in various ways depending on the arrangement of the pixels.

[0169] Since the data line 120 and the first p-type contact electrode layer 25p are elongated in the second direction crossing the first direction, and substantially simultaneously apply the common voltage to the p-type semiconductor layer of the first epitaxial stack 20, the data line 120 and the first

p-type contact electrode layer 25p may be substantially the same component. As such, hereinafter, the first p-type contact electrode layer 25p will be referred to as the data line 120, or vice versa.

[0170] An ohmic electrodes 25p' is disposed in the light emitting area, in which the first p-type contact electrode layer 25p is disposed, for the ohmic contact between the first p-type contact electrode layer 25p and the first epitaxial stack 20. The ohmic electrode 25p' may have various shapes and may be provided in plural. In the illustrated exemplary embodiment, the ohmic electrode 25p' is disposed in an area through which the lower surface of the first epitaxial stack 20 is exposed, however, the inventive concepts are not limited thereto, and the ohmic electrode 25p' may be disposed at another position. The ohmic electrode 25p' for the ohmic contact may include various materials. In an exemplary embodiment, the ohmic electrode 25p' corresponding to a p-type ohmic electrode 25p' may include an Au—Zn alloy or an Au—Be alloy. In this case, since the material for the ohmic electrode 25p' has a reflectivity lower than that of Ag, Al, and Au, an additional reflection electrode may be further disposed, which may include Ag or Au, for example. In this case, a layer including Ti, Ni, Cr, or Ta may be disposed as an adhesive layer for adhesion to adjacent components. For example, the adhesive layer may be deposited thinly on upper and lower surfaces of the reflection electrode including Ag or Au.

[0171] The first n-type contact electrode 21n is disposed on the first epitaxial stack 20. The first scan line  $130_R$  is connected to the first n-type contact electrode 21n. The second n-type contact electrode 3 in is disposed on the second epitaxial stack 30. The second scan line  $130_G$  is connected to the second n-type contact electrode 31n. The third n-type contact electrode 41n is disposed on the third epitaxial stack 40. The third scan line  $130_B$  is connected to the third n-type contact electrode 41n.

[0172] A portion of one side of the second epitaxial stack 30 is removed. A second p-type contact electrode 35pc is disposed on the portion from which the portion of the second epitaxial stack 30 is removed. The second p-type contact electrode 35pc is connected to a first bridge electrode  $BR_G$ , and the first bridge electrode  $BR_G$  is connected to the data line 120 through a first contact hole CH1. A third p-type contact electrode 45pc is connected to a second bridge electrode  $BR_B$ , and the second bridge electrode  $BR_B$  is connected to the data line 120 through a second contact hole CH2. Accordingly, the common voltage is applied to the second and third p-type contact electrodes 35pc and 45pc through the data line 120.

[0173] In an exemplary embodiment, the first, second, and third n-type contact electrodes 21n, 31n, and 41n may include a pad part having a relatively wide area to be easily connected to the first, second, and third scan lines  $130_R$ ,  $130_G$ , and  $130_B$ , respectively, and an extension part extending in one direction from the pad part. The pad part may have various shapes, such as substantially a circular shape, for example. The extension part may assist in providing a uniform current to the n-type semiconductor layer of the first epitaxial stack 20, and may extend in one direction from the pad part. The extension part may have various shapes, such as a substantially elongated shape, for example.

[0174] The adhesive layer, the p-type contact electrode layer, and the wavelength pass filter are disposed between the substrate 10 and each of the first epitaxial stack 20, the

second epitaxial stack 30, and the third epitaxial stack 40. Hereinafter, the pixel according to an exemplary embodiment will be described according to the stacking order.

[0175] The first epitaxial stack 20 is disposed on the substrate 10 with the first adhesive layer 61 interposed therebetween. The first epitaxial stack 20 includes the p-type semiconductor layer, the active layer, and the n-type semiconductor layer, which are sequentially stacked in the upward direction from the lower portion.

[0176] A first insulating layer 81 is disposed on a lower surface, e.g., a surface facing the substrate 10, of the first epitaxial stack 20. The first insulating layer 81 has at least one contact hole. The ohmic electrode 25p' is disposed in the contact hole and makes contact with the p-type semiconductor layer of the first epitaxial stack 20. The ohmic electrode 25p' may include various materials.

[0177] The ohmic electrode 25p' makes contact with the first p-type contact electrode layer 25p (e.g., the data line 120). The first p-type contact electrode layer 25p is disposed between the first insulating layer 81 and the first adhesive layer 61.

[0178] The first p-type contact electrode layer 25p may overlap with the first epitaxial stack 20, more particularly, the light emitting area of the first epitaxial stack 20, and may cover substantial or all of the light emitting area of the first epitaxial stack 20 in a plan view. The first p-type contact electrode layer 25p may include a reflective material that reflects light generated in the first epitaxial stack 20. In addition, the first insulating layer 81 may have reflectivity to enhance the reflection of light in the first epitaxial stack 20. For example, the first insulating layer 81 may have an omni-directional reflector (ODR) structure.